暂存器档案(register file)又称暂存器堆,是CPU中多个暂存器组成的阵列,通常由快速的静态随机读写存储器(SRAM)实现。这种RAM具有专门的读连线埠与写连线埠,可以多路并发访问不同的暂存器。

CPU的指令集架构总是定义了一批暂存器,用于在记忆体与CPU运算部件之间暂存数据。在更为简化的CPU,这些架构暂存器(architectural registers)一一对应与CPU内的物理存在的暂存器。在更为複杂的CPU,使用暂存器重命名技术,使得执行期间哪个架构暂存器对应于哪个暂存器堆的物理存储条目(physical entry stores)是动态改变的。暂存器堆是指令集架构的一部分,程式可以访问,这与透明的CPU高速快取(cache)不同。

基本介绍

- 中文名:暂存器档案

- 外文名:register file

- 又称:暂存器堆

实现

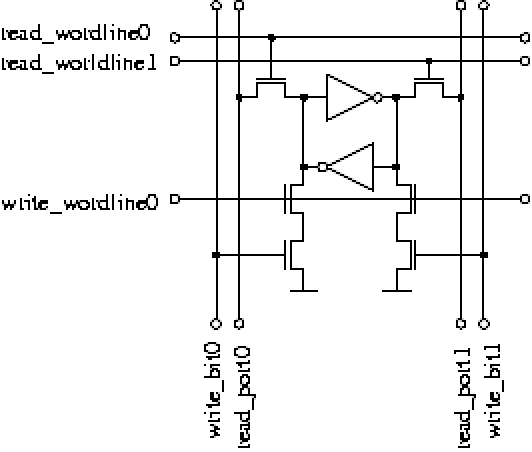

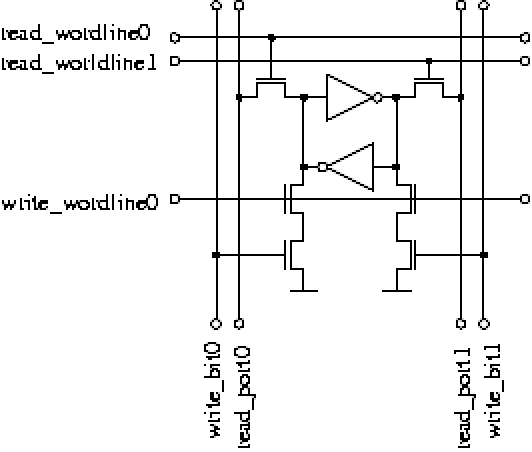

通常的设计布局是一个简单的阵列,在水平方向的一行就是暂存器的全字长宽度,一行的每一位元的存储单元(bit cell)通过位线(Bit Line)读/写其数据。在垂直方向把暂存器一次即能全字长读出。放大电路(Sense amplifier)通常设在底部,把读出的小幅值的两根位线(组成了一对差分电路)的电位差,放大为全幅值的逻辑值电位。更大的暂存器堆的设计是镜像与旋转后(tiling mirrored and rotated)拼贴这种简单的暂存器阵列。

暂存器堆的每个条目(entry,即一个物理暂存器)对每个连线埠(port)都有一条字线(word line),每个位元的基本存储单元,对每个读连线埠有1条位线,对每个写连线埠有2条位线。每个位元的基本存储单元都连线到了供电的Vdd(高电平)与Vss(低电平或者接地),这里的d是指组成SRAM的场效应管的漏极(drain),s是指场效应管的源极(source)。因此,布线所占面积随连线埠的平方增加,电晶体是线性增加。多个冗余的具有较少读连线埠的暂存器堆可能会比具有全套多个读连线埠的单一暂存器堆,面积更小、读取更快。MIPSR8000的整数单元,有一个暂存器堆的实现,有32个条目,字长64位,具有9个读连线埠及4个写连线埠。 一个典型的暂存器堆

一个典型的暂存器堆

一个典型的暂存器堆

一个典型的暂存器堆解码

- 解码器经常划分为预解码(predecoder)与解码(decoder)。

- 解码器是一系列的与门,最终选定并驱动字线。

- 每个读连线埠与写连线埠都有自己的专用解码器。例如,如果阵列有4个读连线埠与2个写连线埠,那幺就有6套地址解码器,每个暂存器堆的条目有6条字线。

阵列

一个位元的基本存储单元的基本模式:

- 状态被存储在一对反相器中;

- 数据通过一个NMOS电晶体取到与字线相配的“读位线”上。

- 数据通过“写位线”的电位来控制2个作为开关的NMOS管导通或者截止,从而把反相器的一端或者另外一端接地来写入数据。

- 因此:读连线埠需要一个电晶体,而写连线埠需要4个电晶体!

许多可能的最佳化:

- 在基本存储单元之间共享线路,如Vdd与Vss电源线。

- 读位线经常预充为Vdd或者Vss。

- 读位线经常是在Vdd或Vss电位附近的一个小幅值内波动来表示存储的状态。由感知放大器把这种小幅值信号变换为全幅值的逻辑信号。小幅值信号的速度更快,因为位线仅有很小的驱动但是具有很大的寄生电容。

- 写位线是全幅值信号,这可能会导致与它伴生走线的读位线的很大干扰。

- 如果Vdd是平行走线可以关闭,如果这个周期内一个写连线埠正在写入。这种最佳化提高了写速度。

- 採用低功率电子设备来降低能耗

微架构

大多数暂存器堆并没有特殊设施来预防多个写连线埠同时写同一个暂存器条目。替代的,指令调度硬体确保在任何时钟周期只有一条指令写入特定的一个暂存器条目。如果针对同一个暂存器的多条机器指令同时被发出(issue),只有一条的写使能(write enable)不被关闭。

每个基本存储单元内部的两个交叉反相器需要在写位线执行后用一些时间修改内部状态。如果正在写操作时对同一个条目执行读操作,或者需要等待更长时间,或者读到的是错误的状态数据。通常有一个旁路复用器(bypass multiplexor)把正在写入的数据旁路(bypass)给读连线埠。 这种旁路复用器往往是更大规模旁路网路的一部分,用来把功能器件之间转发还没有提交的数据。

暂存器堆通常是间距匹配与所对应的数据通路,这避免了许多汇流排转角,节约了占用面积。但是由于每个单元必须有相同的位线间距,迫使数据通路上的位线间距遵从最宽的单元,浪费了面积。

如果一条数据通路经过多个单元,则通过两条数据通路并行,使得每条数据通路的位线间距更小,从而节约了面积。因此通常会导致了一个暂存器堆的多个副本,每个副本有自己的数据通路。

例如,Alpha 21264(EV6)处理器有两个整数暂存器堆的副本。仅用一个时钟周期就可以在二者之间传播数据。发射逻辑(issue logic)试图降低在两个副本间的数据转发。MIPSR8000浮点单元有两个浮点暂存器堆的副本,每个副本有4个读口、4个写口。写操作是对两个副本的对应条目同时写入。

处理器的暂存器重命名能为每个功能单元安排写入到物理暂存器堆的一个子集。这可以避免每个基本存储单元有多个写口的要求,很大节约了面积。最终的暂存器堆,效果上是一个单写口、双读口的暂存器堆组成的栈。

SPARCISA定义了“register window”,暂存器的5-bit架构名称指向一个很大的有数百个条目的暂存器堆的一个视窗。register window没移动一步就经过16个暂存器。因此每个架构暂存器名字仅指向这个暂存器堆中的少量暂存器。例如架构暂存器r20仅指向物理暂存器#20, #36, #52, #68, #84, #100, #116, 如果这个物理暂存器堆仅有7个视窗。